Z80 CPU failure mode: unable to single step past first instruction

This is a description of a failure mode I encountered while building a circuit around the Z80 microprocessor. I spent several hours on trying to debug my circuit only to discover that the CPU itself was faulty.

The difficulty came from the fact that the CPU did execute M1-only instructions successfully, yet failed after successfully executing the first instruction which required M2 machine cycles (memory read).

Another difference was the current draw: the bad CPU drew 190mA and a good one draws 70mA with the exact setup. The exact CPU type is Z84C0020PEC, CMOS.

One last difference I noted was that this caused high output pins to only be brought up to about 3V, instead of the 5V I'm reading on a good CPU.

I've wired up a simple Z80 circuit, and I've encountered a strange issue: after successfully executing one instruction, the M1 cycle of the NEXT instruction never completes successfully.

The difficulty came from the fact that the CPU did execute M1-only instructions successfully, yet failed after successfully executing the first instruction which required M2 machine cycles (memory read).

Another difference was the current draw: the bad CPU drew 190mA and a good one draws 70mA with the exact setup. The exact CPU type is Z84C0020PEC, CMOS.

One last difference I noted was that this caused high output pins to only be brought up to about 3V, instead of the 5V I'm reading on a good CPU.

Here are some facts:

- I can execute indefinitely many M1-only instructions (such as: NOP, INC r)

- As soon as an instruction which has an M2 cycle as well (such as JP nn), only the FIRST such instruction is executed successfully; a second one enters a "corrupted" M1 cycle which never finishes.

My test setup

- manual clock, using a Schmitt Trigger to clean up the edges; this is reliable, as I can accurately move from one Tstate to the next

- Hard wire 11000011b (0xC3) on data lines; this is intended to run as JP 0xC3C3. Z80 manual says this is a 10-clock operation (4, 3, 3)

My reproduction steps

- Verify 0 on A0-A7 (to fetch opcode byte)

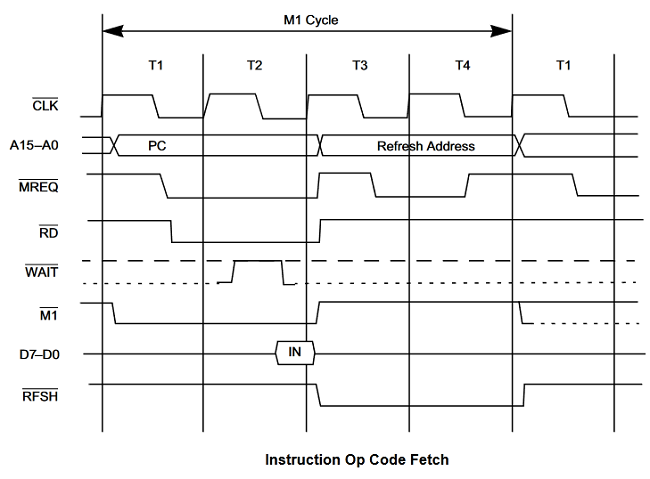

- Run through M1 (4 clocks) and compare successfully to spec timing diagram at each clock cycle

- Verify 1 on A0-A7 (to fetch first byte of operand)

- Run through M2 (3 clocks) and compare successfully to spec timing diagram at each clock cycle

- Verify 2 on A0-A7 (to fetch second byte of operand)

- Run through M2 (3 clocks) and compare successfully to spec timing diagram at each clock cycle

- Verify 11000011 on A0-A7

(At this point, since C3 is present on A0-A7, it proves that the CPU has executed the first JP 0xC3C3 successfully.)

- Verify output voltages correspond to beginning of M1

- Try executing the second JP 0xC3C3

- Failure: partway (T3 high clock) through M1, output voltages no longer match Z80 spec's M1 timing diagram and CPU is stuck in a repeating pattern.

I am able to reproduce this every single time I run this test. First JP nn is always successful, second instruction fails.

Here is my observed timing of second instruction. Here is the timing I get, from the start of the second JP nn. My timing matches the spec timing only during T1 and T2.